SKYPER®

### Driver Core

Order Number L5063103 Datasheet valid for L5063103 Index 08

### SKYPER 42 LJ R (coated)

Characteristics

t<sub>d(on.dia)</sub>

t<sub>d(off,ana)</sub>

t<sub>d(off,dig)</sub>

RIN(err,prim)

CIN(err,prim)

#### Features\*

- Two output channels

- · Integrated power supply

- Separated failure/signal transmission ٠

- Selectable dead time

- Dynamic short-circuit detection ٠

- · SoftOff in error condition

- Active clamping

- · Selectable filter setting

- Multi failure management

- ROHS, UL recognized •

- Coated with SL1307

#### Typical Applications

• Driver for IGBT modules in bridge circuits in industrial application

#### Remarks

- · The insulation test is not performed as 100% series test at SEMIKRON

- The maximum DC-Link voltage is limited by the creepage and clearance distances; according to EN50178-1, PD II, OVC III

- · Operating temperature is real ambient temperature around the driver core

- Environmental conditions see **Technical Explanation**

- Do not touch the transformers

| Absolute Maximum Ratings |                                                            |           |       |  |

|--------------------------|------------------------------------------------------------|-----------|-------|--|

| Symbol                   | Conditions                                                 | Values    | Unit  |  |

|                          |                                                            |           |       |  |

| Vs                       | Supply voltage primary side                                | 15.6      | V     |  |

| V <sub>IH</sub>          | Input signal voltage (HIGH)                                | Vs + 0.3  | V     |  |

| V <sub>IL</sub>          | Input signal voltage (LOW)                                 | GND - 0.3 | V     |  |

| I <sub>out(peak)</sub>   | Output peak current <sup>1)</sup>                          | 24        | А     |  |

| Iout(avg)                | Output average current <sup>1)</sup>                       | 120       | mA    |  |

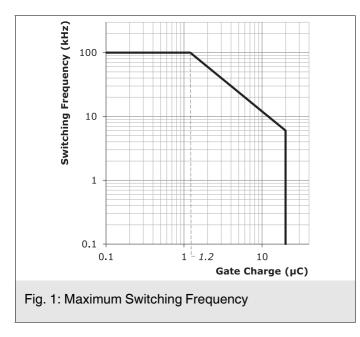

| f <sub>max</sub>         | Maximum switching frequency <sup>2)</sup>                  | 100       | kHz   |  |

| V <sub>CE</sub>          | Collector emitter voltage <sup>3)</sup>                    | 1700      | V     |  |

| V <sub>DC</sub>          | DC-Link voltage <sup>4)</sup>                              | 1200      | V     |  |

| dv/dt                    | Rate of rise and fall of voltage secondary to primary side | 100       | kV/μs |  |

| V <sub>isol</sub>        | Insulation test voltage <sup>5)</sup>                      | 4000      | V     |  |

| Q <sub>out</sub>         | Output charge per pulse <sup>6)</sup>                      | 20        | μC    |  |

| T <sub>op</sub>          | Operating temperature range                                | -40 85    | °C    |  |

| T <sub>stg</sub>         | Storage temperature range                                  | -40 85    | °C    |  |

#### Symbol Conditions min. max. Unit typ. Vs 15.6 Supply voltage primary side 144 15 Primary side undervoltage-lockout V<sub>UVLO(prim)</sub> 12.2 shutdown threshold Primary side undervoltage-lockout 13.9 reset threshold Secondary side undervoltage-lockout shutdown threshold, positive gate 9.4 VUVLO(secP) voltage Secondary side undervoltage-lockout 13.3 reset threshold, positive gate voltage Secondary side undervoltage-lockout shutdown threshold, negative gate -4.1 V<sub>UVLO(secN)</sub> voltage Secondary side undervoltage-lockout -5.8 reset threshold, negative gate voltage Supply current primary side (no load) 65 mA I<sub>S(idle)</sub> Supply current primary side (full load) 700 mΑ I<sub>S(max)</sub> VI Input signal voltage on/off Vs/0 VIT+ Input threshold voltage (HIGH) 8.6 VIT-Input threshold voltage (LOW) 6.7 Input resistance (switching signals) 33 kΩ RIN(sw) Input capacitance (switching signals) 0.01 CIN(sw) nF Turn-on output voltage 14.8 V<sub>G(on)</sub> V<sub>G(off)</sub> Turn-off output voltage -8 Turn-on propagation delay time 0.5 t<sub>d(on,ana)</sub> μs for analog filter selection Turn-on propagation delay time

for digital filter selection Turn-off propagation delay time

for analog filter selection Turn-off propagation delay time

for digital filter selection Input resistance

(error input, primary side) Input capacitance

(error input, primary side)

V

V

V

V

v

V

v

V

v

v

v

٧

μs

μs

μs

kΩ

nF

0.83

0.5

0.83

150

10

### **SKYPER**<sup>®</sup>

### **Driver** Core

Order Number L5063103 Datasheet valid for L5063103 Index 08

### SKYPER 42 LJ R (coated)

#### Features\*

- Two output channels

- Integrated power supply

- Separated failure/signal transmission

- Selectable dead time

- Dynamic short-circuit detection

- SoftOff in error condition

- Active clamping

- Selectable filter setting

- Multi failure management

- ROHS, UL recognized

- Coated with SL1307

#### **Typical Applications**

Driver for IGBT modules in bridge circuits in industrial application

#### Remarks

- The insulation test is not performed as 100% series test at SEMIKRON

- The maximum DC-Link voltage is limited by the creepage and clearance distances; according to EN50178-1, PD II, OVC III

- Operating temperature is real ambient temperature around the driver core

- Environmental conditions see Technical Explanation

- Do not touch the transformers

| Characteristics          |                                                                                       |        |      |      |                   |

|--------------------------|---------------------------------------------------------------------------------------|--------|------|------|-------------------|

| Symbol                   | Conditions                                                                            | min.   | typ. | max. | Unit              |

| R <sub>IN(err,sec)</sub> | Input resistance<br>(error inputs, secondary side)                                    |        | 150  |      | kΩ                |

| C <sub>IN(err,sec)</sub> | Input capacitance<br>(error inputs, secondary side)                                   |        |      | 0.01 | nF                |

| t <sub>d(err)</sub>      | Error propagation delay time <sup>7)</sup>                                            |        | 0.7  |      | μs                |

| t <sub>d(err,ext)</sub>  | External error propagation delay time <sup>8)</sup>                                   |        | 0.6  |      | μs                |

| t <sub>IDT</sub>         | Interlock dead time9)                                                                 |        | 2    |      | μs                |

| t <sub>jitter(ana)</sub> | Signal transfer deviation for analog filter selection <sup>10)</sup>                  |        | ± 3  |      | ns                |

| t <sub>jitter(dig)</sub> | Signal transfer deviation for digital filter selection <sup>10)</sup>                 | ± 12.5 |      |      | ns                |

| t <sub>SPS(ana)</sub>    | Short pulse suppression<br>for analog filter selection                                | 0.2    |      |      | μs                |

| t <sub>SPS(dig)</sub>    | Short pulse suppression<br>for digital filter selection                               | 0.39   |      |      | μs                |

| t <sub>POR</sub>         | Power-on reset time                                                                   |        | 0.15 |      | S                 |

| t <sub>reset</sub>       | Error reset time <sup>11)</sup>                                                       | 0.03   |      |      | ms                |

| V <sub>CE(ref)</sub>     | Reference voltage for<br>V <sub>CE</sub> -monitoring <sup>12)</sup>                   |        |      | 9    | v                 |

| VITH(clamp)              | Input threshold voltage clamping (HIGH) <sup>13)</sup>                                |        |      | 13   | V                 |

| V <sub>ITL(clamp)</sub>  | Input threshold voltage clamping (LOW) <sup>13)</sup>                                 | 2      |      |      | V                 |

| R <sub>IN(clamp)</sub>   | Input resistance (clamping inputs)                                                    |        | 150  |      | kΩ                |

| C <sub>IN(clamp)</sub>   | Input capacitance (clamping inputs)                                                   |        |      | 0.01 | nF                |

| I <sub>clear(PS)</sub>   | Shortest distance in air, primary side to secondary side                              | 12.2   |      |      | mm                |

| I <sub>clear(SS)</sub>   | Shortest distance in air, secondary sides                                             | 6.1    |      |      | mm                |

| I <sub>creep(PS)</sub>   | Shortest distance along the surface,<br>primary side to secondary side<br>(CTI > 175) | 12.2   |      |      | mm                |

| I <sub>creep(SS)</sub>   | Shortest distance along the surface,<br>secondary sides<br>(CTI > 175)                | 6.1    |      |      | mm                |

| V <sub>imp</sub>         | Impulse withstand voltage <sup>14)</sup>                                              | 8000   |      |      | V                 |

| V <sub>PDPS</sub>        | Partial discharge extinction voltage, primary side to secondary side <sup>15)</sup>   | 2107   |      | V    |                   |

| w                        | Weight                                                                                |        | 22   |      | g                 |

| MTBF                     | Mean Time Between Failure <sup>16)</sup>                                              |        | 7.5  |      | 10 <sup>6</sup> ł |

#### Footnotes

| Footnote | Description                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1)       | The rated peak and average output current are valid over the full operating temperature range.                                                                                                                                                                                                                                                                                                    |  |  |

| 2)       | The rated maximum switching frequency is valid over the full operating temperature range.                                                                                                                                                                                                                                                                                                         |  |  |

| 3)       | Repetitive peak voltage across the semiconductor power rails.                                                                                                                                                                                                                                                                                                                                     |  |  |

| 4)       | The maximum DC-Link voltage is limited by creepage and clearance distances (according to EN50178-1, PD II, OVC III).                                                                                                                                                                                                                                                                              |  |  |

| 5)       | Test Conditions: ACrms, 2s, input to output.                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 6)       | If using power semiconductor modules with gate charges >2.5µC, the buffer capacitance of the driver's secondary sides and primary side has to be adjusted according to the corresponding Technical Explanation.                                                                                                                                                                                   |  |  |

| 7)       | Time between the driver detects an error at the secondary side until the primary side reports an error at the interface.                                                                                                                                                                                                                                                                          |  |  |

| 8)       | Time between the driver receives an external error signal at the primary side until the driver turns off its outputs at the secondary side.                                                                                                                                                                                                                                                       |  |  |

| 9)       | The interlock dead time prevents the two outputs from being activated simultaneously. The dead time generation starts with each turn-off command at the driver's primary side. The interlock dead time generation could be deactivated via pin 'CFG_IDT'.                                                                                                                                         |  |  |

| 10)      | The jitter is defined as the maximum deviation of the switching signal propagation delay time at constant environmental conditions. The signal transfer deviation t <sub>jitter(ana)</sub> is valid if analog filtering is selected via pin 'CFG_FLT' and the interlock dead time, generated by the controller, is longer than the interlock dead time which is ensured by the driver itself.     |  |  |

| 11)      | Minimum time for which the driver is in error state.                                                                                                                                                                                                                                                                                                                                              |  |  |

| 12)      | The driver detects a desaturation event, when one of its outputs is in on-state and the applied voltage at the corresponding V <sub>CE</sub> -monitoring input (pin 'VCE_IN') exceeds the reference voltage for V <sub>CE</sub> -monitoring. As long as the blanking time has not been elapsed, the desaturation detection is deactivated. The blanking time is adjustable via the 'CFG_VCE' pin. |  |  |

| 13)      | The driver's output switches to high-resistance state, when the output is in off-state and the applied voltage at the corresponding 'CLMP_IN' pin exceeds the input threshold voltage V <sub>ITH(clamp)</sub> . The output returns to off-state when the applied voltage at pin 'CLMP_IN' falls below the input threshold voltage V <sub>ITL(clamp)</sub> .                                       |  |  |

| 14)      | Test condition: 8000V, pulse according to EN50178-1.                                                                                                                                                                                                                                                                                                                                              |  |  |

| 15)      | The partial discharge extinction voltage in this data sheet is defined as peak voltage.                                                                                                                                                                                                                                                                                                           |  |  |

| 16)      | Conditions: $T_{op} = 40^{\circ}$ C; full load. Theoretical consideration according to SN 29500.                                                                                                                                                                                                                                                                                                  |  |  |

| 17)      | All external circuits, except the V <sub>CE</sub> reference voltage adjustment, have to be supplied via pin 'PWR_VS_P_OUT' with respect to pin 'PWR_VS_N_OUT'. The rated average output current is reduced by the supply current of these external circuits.                                                                                                                                      |  |  |

#### Pin description - primary side

| PIN    | Signal   | Function                                                        | Specifications                                                                                                                                     |

|--------|----------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| X10:01 | PWR_GND  | Ground potential for power supply and digital signals           | To be connected to ground                                                                                                                          |

| X10:02 | CFG_IDT  | Interlock dead time configuration                               | 15V logic; 150kΩ (pull-up)<br>LOW = 2µs interlock dead time<br>HIGH = No interlock dead time                                                       |

| X10:03 | nERR_OUT | Error output                                                    | Open collector output; max. 18V/15mA<br>(external pull-up resistor needed)<br>LOW = Error<br>HIGH = No error                                       |

| X10:04 | nERR_IN  | Error input                                                     | 15V logic inverted; 150kΩ/10nF (pull-up)<br>LOW = External error<br>HIGH = No external error                                                       |

| X10:05 | CFG_ERR  | Error behavior configuration<br>in case of secondary side error | 15V logic; 150kΩ (pull-down)<br>LOW = Both outputs switch off<br>HIGH = Outputs switch off with next turn-off<br>signal at the corresponding input |

| X10:06 | CFG_FLT  | Filter configuration<br>for switching signals                   | 15V logic; 150kΩ (pull-down)<br>LOW = Analog filter ( $t_{SPS(ana)}$ )<br>HIGH = Digital filter ( $t_{SPS(dig)}$ )                                 |

| X10:07 | TOP_IN   | Switching signal input (TOP)                                    | 15V logic; 33kΩ/0.01nF (pull-down)<br>LOW = TOP switch off<br>HIGH = TOP switch on                                                                 |

| X10:08 | BOT_IN   | Switching signal input (BOT)                                    | 15V logic; 33kΩ/0.01nF (pull-down)<br>LOW = BOT switch off<br>HIGH = BOT switch on                                                                 |

| X10:09 | PWR_VS   | Driver power supply                                             | Stabilized +15V ±4%                                                                                                                                |

| X10:10 | PWR_VS   | Driver power supply                                             | Stabilized +15V ±4%                                                                                                                                |

#### Pin description - secondary side - TOP

| PIN     | Signal       | Function                                              | Specifications                                                                                                                                                                        |

|---------|--------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X100:01 | CFG_VCE      | V <sub>CE</sub> -monitoring reference voltage         | External voltage divider needed                                                                                                                                                       |

| X100:02 | VCE_IN       | V <sub>CE</sub> -monitoring input                     | External blocking diode needed                                                                                                                                                        |

| X100:03 | PWR_VS_P_OUT | Power supply output, positive voltage                 | Equal to $V_{G(on)}^{17)}$ (external buffer capacitors can be connected)                                                                                                              |

| X100:04 | nERR_IN      | External error input                                  | 15V logic inverted; 150kΩ/0.01nF (pull-up)<br>LOW = External error<br>HIGH = No external error                                                                                        |

| X100:05 | TOP_ON       | On signal path to TOP semiconductor                   | $\begin{array}{l} \mbox{External gate resistor needed} \\ (\mbox{in consideration of } I_{\mbox{out}(\mbox{avg})}, I_{\mbox{out}(\mbox{peak})}, V_{\mbox{G}(\mbox{on})}) \end{array}$ |

| X100:06 | TOP_OFF      | Off signal path to TOP semiconductor                  | $\begin{array}{l} \mbox{External gate resistor needed} \\ (\mbox{in consideration of -}I_{out(avg)}, -I_{out(peak)}, V_{G(off)}) \end{array}$                                         |

| X100:07 | CLMP_IN      | V <sub>CE</sub> -clamping input                       | 150kΩ/0.01nF (pull-down)<br>In case of activated TOP_OFF:<br>LOW = TOP_OFF equal to $V_{G(off)}$<br>HIGH = TOP_OFF floating                                                           |

| X100:08 | PWR_GND      | Ground potential for power supply and digital signals | Reference potential for gate voltages<br>(emitter/source of power semiconductor)                                                                                                      |

| X100:09 | TOP_SOFTOFF  | SoftOff signal path to TOP semiconductor              | External gate resistor needed                                                                                                                                                         |

| X100:10 | PWR_VS_N_OUT | Power supply output, negative voltage                 | Equal to $V_{G(off)}^{17)}$ (external buffer capacitors can be connected)                                                                                                             |

| PIN     | Signal       | Function                                              | Specifications                                                                                                                                                        |

|---------|--------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X200:01 | CFG_VCE      | V <sub>CE</sub> -monitoring reference voltage         | External voltage divider needed                                                                                                                                       |

| X200:02 | VCE_IN       | V <sub>CE</sub> -monitoring input                     | External blocking diode needed                                                                                                                                        |

| X200:03 | PWR_VS_P_OUT | Power supply output, positive voltage                 | Equal to $V_{G(on)}^{17)}$ (external buffer capacitors can be connected)                                                                                              |

| X200:04 | nERR_IN      | External error input                                  | 15V logic inverted; 150kΩ/0.01nF (pull-up)<br>LOW = External error<br>HIGH = No external error                                                                        |

| X200:05 | BOT_ON       | On signal path to BOT semiconductor                   | $\label{eq:constraint} \begin{array}{c} \mbox{External gate resistor needed} \\ \mbox{(in consideration of } I_{out(avg)}, \ I_{out(peak)}, \ V_{G(on)}) \end{array}$ |

| X200:06 | BOT_OFF      | Off signal path to BOT semiconductor                  | External gate resistor needed<br>(in consideration of -I <sub>out(avg)</sub> , -I <sub>out(peak)</sub> , V <sub>G(off)</sub> )                                        |

| X200:07 | CLMP_IN      | V <sub>CE</sub> -clamping input                       | 150kΩ/0.01nF (pull-down)<br>In case of activated BOT_OFF:<br>LOW = BOT_OFF equal to $V_{G(off)}$<br>HIGH = BOT_OFF floating                                           |

| X200:08 | PWR_GND      | Ground potential for power supply and digital signals | Reference potential for gate voltages<br>(emitter/source of power semiconductor)                                                                                      |

| X200:09 | BOT_SOFTOFF  | SoftOff signal path to BOT semiconductor              | External gate resistor needed                                                                                                                                         |

| X200:10 | PWR_VS_N_OUT | Power supply output, negative voltage                 | Equal to $V_{G(off)}^{17)}$ (external buffer capacitors can be connected)                                                                                             |

#### Pin description - secondary side - BOT

This is an electrostatic discharge sensitive device (ESDS) due to international standard IEC 61340.

#### **\*IMPORTANT INFORMATION AND WARNINGS**

The specifications of SEMIKRON products may not be considered as guarantee or assurance of product characteristics ("Beschaffenheitsgarantie"). The specifications of SEMIKRON products describe only the usual characteristics of products to be expected in typical applications, which may still vary depending on the specific application. Therefore, products must be tested for the respective application in advance. Application adjustments may be necessary. The user of SEMIKRON products is responsible for the safety of their applications embedding SEMIKRON products and must take adequate safety measures to prevent the applications from causing a physical injury, fire or other problem if any of SEMIKRON products become faulty. The user is responsible to make sure that the application design is compliant with all applicable laws, regulations, norms and standards. Except as otherwise explicitly approved by SEMIKRON in a written document signed by authorized representatives of SEMIKRON, SEMIKRON products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury. No representation or warranty is given and no liability is assumed with respect to the accuracy, completeness and/or use of any information herein, including without limitation, warranties of non-infringement of intellectual property rights of any third party. SEMIKRON does not assume any liability arising out of the applications or use of any product; neither does it convey any license under its patent rights, copyrights, trade secrets or other intellectual property rights, nor the rights of others. SEMIKRON makes no representation or warranty of non-infringement or alleged non-infringement of intellectual property rights of any third party which may arise from applications. Due to technical requirements our products may contain dangerous substances. For information on the types in question please contact the nearest SEMIKRON sales office. This document supersedes and replaces all information previously supplied and may be superseded by updates. SEMIKRON reserves the right to make changes.